### [제23회 한국반도체학술대회\_Program at a Glance]

|  | 2월 22일(월)   | Roc          | m A               | Roc              | om B   |        |        |        |        |        |        |        |  |

|--|-------------|--------------|-------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|--|

|  | 28 228(8)   | 태백름(5층)      |                   | 함백룸(5층)          |        | ]      |        |        |        |        |        |        |  |

|  | 14:00-18:00 | [Short C     | ourse 1]          | [Short Course 2] |        | ]      |        |        |        |        |        |        |  |

|  |             | 3차원 집적 기술:   |                   | 차세대 저전력소자의       |        |        |        |        |        |        |        |        |  |

|  |             | 원리의          | 박 <del>응용</del>   | 개발고              | 박 설계   |        |        |        |        |        |        |        |  |

|  |             |              |                   |                  |        | -      |        |        |        |        |        |        |  |

|  | 2월 23일(화)   | Room A       | Room B            | Room C           | Room D | Room E | Room F | Room G | Room H | Room I | Room J | Room K |  |

|  |             |              |                   | 5층               |        |        | 6층     |        |        |        |        |        |  |

|  |             | सथ् <u>म</u> | <b>ध</b> ्ध्या+ाग | 함백I              | 함백Ⅱ+Ⅲ  | 컨벤션홀L  | 봉래I    | 봉래Ⅱ+Ⅲ  | 육백I    | 육백Ⅱ    | 청옥I    | 청옥Ⅱ+Ⅲ  |  |

|  |             |              |                   |                  |        |        |        |        |        |        |        |        |  |

| 2월 23일(화)   |                                                                                                                  |                                         | 58                                                 |                                                                                        |                     | 68                                          |                                                    |                                                  |                                     |                                                      |                                                       |                |

|-------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|---------------------------------------------|----------------------------------------------------|--------------------------------------------------|-------------------------------------|------------------------------------------------------|-------------------------------------------------------|----------------|

|             | el था                                                                                                            | <b>ध्य थ्य</b> ∏+Ⅲ                      | 함백I                                                | 함백Ⅱ+Ⅲ                                                                                  | 컨벤션홀니               | 봉래I                                         | 봉래II+III                                           | 육백I                                              | 육백Ⅱ                                 | 청옥I                                                  | 청옥Ⅱ+Ⅲ                                                 | 로비             |

|             | [TA1-L]                                                                                                          | [TB1-D]                                 | [TC1-F]                                            | [TD1-G]                                                                                |                     | [TF1-I]                                     | [TG1-F]                                            | [TH1-J]                                          |                                     | [TJ1-K]                                              | [TK1-R]                                               |                |

| 08:30-10:30 | Analog Design I                                                                                                  | 1D/2D Materials<br>& Devices            | Novel Si Devices<br>and Integrated<br>Circuits (4) | Device Physics<br>and<br>Characterization<br>1 : Field-effect                          |                     | High efficiency<br>sensors and<br>devices   | Novel Si Devices<br>and Integrated<br>Circuits (1) | Nanofabrication<br>for Application               |                                     | Memory<br>processing and<br>RRAM operation           | Interaction of<br>system SW and<br>semiconductor      |                |

| 10:30-10:40 | 휴식 (& 커피, 다과)                                                                                                    |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     |                                                      |                                                       |                |

|             | [TA2-L]                                                                                                          | [TB2-D]                                 | [TC2-M]                                            | [TD2-G]                                                                                |                     | [TF2-O]                                     | [TG2-F]                                            | [TH2-J]                                          | CDC                                 | [TJ2-K]                                              | [TK2-R]                                               |                |

| 10:40-12:40 | Analog Design II                                                                                                 | Oxide<br>Semiconductors                 | RFIC and smart<br>RFID tags                        | Reliability<br>Analysis : Thin-<br>film transistors<br>and field-effect<br>transistors |                     | VLSI System<br>Design for<br>Communications | Novel Si Devices<br>and Integrated<br>Circuits (2) | Nanofabrication<br>for Application               |                                     | NAND, PCRAM,<br>and MRAM                             | Little more<br>faster, and even<br>better reliability |                |

| 12:40-13:40 |                                                                                                                  |                                         | •                                                  | 점심 [포레스                                                                                | 트볼룸 / 4층]           |                                             |                                                    |                                                  |                                     |                                                      |                                                       | Chip<br>Design |

| 13:40-14:20 | 기초강연 1 : Prof. Akira Toriumi (The University of Tokyo) CC                                                        |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     | Contest<br>& 전시                                      |                                                       |                |

| 14:20-15:00 | 기조강연 2 : 박재근 교수 (한양대학교)<br>" Nonvolatile Memory Technology beyond 20nm : Dilemma & Challenge"<br>[컨벤션홈 K+W / 5종] |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     |                                                      |                                                       |                |

| 15:00-15:10 | 휴식 (& 커피, 다과)                                                                                                    |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     |                                                      |                                                       |                |

|             | [TA3-A]                                                                                                          | [TB3-D]                                 | [ТСЗ-Н]                                            | [TD3-G]                                                                                |                     | [TF3-Q]                                     | [TG3-F]                                            | [TH3-J]                                          | [T11-N]                             | [ТЈЗ-К]                                              | [ТКЗ-Е]                                               |                |

| 15:10-17:10 | A2: Enabling<br>packaging<br>technologies                                                                        | Process<br>Technology for<br>Thin Films | Display and<br>Imaging<br>Technologies             | Device Modeling<br>and Simulation 1<br>: RF, teraherz,<br>low-power, and               |                     | Metrology and<br>Inspection I               | Novel Si Devices<br>and Integrated<br>Circuits (3) | Graphene and<br>Related Carbon<br>Nanostructures | Advances in<br>Design<br>Technology | Circuit related<br>topics and<br>memory<br>selectors | Advanced GaN<br>Technology                            |                |

| 17:10-18:30 |                                                                                                                  |                                         |                                                    |                                                                                        | 포스터<br>세션1<br>[TP1] |                                             |                                                    |                                                  | •                                   |                                                      |                                                       |                |

| 18:30-20:00 | 만찬 [컨벤션홈 K+W / 5종]                                                                                               |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     |                                                      |                                                       |                |

| 20:00-      | Rump Session 1 : 스케일링 한게 극복을 위한 미레 반도체 기술 [태백통 / 5중]<br>Rump Session 2 : 초연결 사회의 반도체 기술 진망과 과제 [함백통 / 5중]        |                                         |                                                    |                                                                                        |                     |                                             |                                                    |                                                  |                                     |                                                      |                                                       |                |

Room L

|             | Room A                                                                     | Room B                                  | Room C                                                                    | Room D                                                                         | Room E              | Room F                                    | Room G                                      | Room H                                                 | Room I                                      | Room J                                                                  | Room K              | Room L |

|-------------|----------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------|-------------------------------------------|---------------------------------------------|--------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------|---------------------|--------|

| 2월 24일(수)   | 5층                                                                         |                                         |                                                                           |                                                                                |                     | 6충                                        |                                             |                                                        |                                             |                                                                         |                     | 5층     |

|             | ध्रम्<br>सम्ब                                                              | <b>ध्र</b> थ्∏+Ⅲ                        | 함백I                                                                       | 함백Ⅱ+Ⅲ                                                                          | 컨벤션홀L               | 봉래I                                       | 봉래Ⅱ+Ⅲ                                       | 육백I                                                    | 육백II                                        | 청옥I                                                                     | 청옥표+표               | 로비     |

|             | [WA1-A]                                                                    | [WB1-D]                                 | [WC1-C]                                                                   | [WD1-G]                                                                        |                     | [WF1-Q]                                   | [WG1-F]                                     | [WH1-J]                                                | [WI1-N]                                     | [WJ1-K]                                                                 | [WK1-E]             |        |

| 08:30-10:00 | A1: Contact and<br>thin film<br>technologies for<br>high<br>performance    | Thin Films for<br>Emerging<br>Devices I | Materials Growth<br>&<br>Characterization<br>: Emerging new<br>electrical | and                                                                            |                     | Metrology and<br>Inspection II            | Materials and<br>Processing<br>Technologies | Two-<br>Dimensional<br>Materials<br>beyond<br>Graphene | Architecture-<br>Level Design<br>Techniques | Unconventional<br>approaches in<br>memory<br>research                   | GaN Power<br>Device |        |

| 10:00-10:10 | 휴식 (& 커피, 다과)                                                              |                                         |                                                                           |                                                                                |                     |                                           |                                             |                                                        | 1                                           |                                                                         |                     |        |

|             | [WA2-A]                                                                    | [WB2-D]                                 | [WC2-C]                                                                   | [WD2-G]                                                                        |                     | [WF2-0]                                   | [WG2-F]                                     | [WH2-J]                                                | [WI2-B]                                     | [WJ2-P]                                                                 | [WK2-E]             | 전시     |

| 10:10-11:40 | A3: Novel<br>interconnect and<br>packaging<br>technologies for<br>emerging | Thin Films for                          | Materials Growth<br>&<br>Characterization<br>: III-Nitrides and<br>Si     | Device<br>Modeling and<br>Simulation 2 :<br>Ab-initio and<br>theoretical study |                     | VLSI System<br>Design and<br>Applications | Si and Group-IV<br>Photonics                | Two-<br>Dimensional<br>Materials /<br>Spintronics      | Patterning                                  | Device for<br>Energy (Solar<br>Cell, Power<br>Device, Battery,<br>etc.) | III-V Device        |        |

| 11:40-13:00 |                                                                            |                                         |                                                                           |                                                                                | 포스터<br>세션2<br>[WP1] |                                           |                                             |                                                        |                                             |                                                                         |                     |        |

| 13:00-      | 점심 [포레스트볼륨 / 4층]                                                           |                                         |                                                                           |                                                                                |                     |                                           |                                             |                                                        |                                             |                                                                         |                     |        |

The 23<sup>rd</sup> Korean Conference on Semiconductors (KCS 2016)

# 제23회 한국반도체학술대회

2016년 2월 22일(월)-24일(수), 강원도 하이원리조트

#### N. VLSI CAD 분과

Room I 육백ㅍ(6층)

# 2016년 2월 24일(수) 08:30-10:00 [WI1-N] Architecture-Level Design Techniques 좌장 : 이종은(UNIST), 정재용(인천대학교)

| WI1-N-1 | 08:30-08:45 | Power-Optimized Design of N:1 Serializer in 65-nm CMOS<br>Tongsung Kim and Woo-Young Choi<br>Department of Electrical and Electronic Engineering, Yonsei University                                                                                                                                |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WI1-N-2 | 08:45-09:00 | CAM Structure of Built-in Redundancy Analysis Hardware<br>Jooyoung Kim, Keewon Cho, Woosung Lee, Soyeon Kang, and<br>Sungho Kang<br>Department of Electrical and Electronic Engineering, Yonsei University                                                                                         |

| WI1-N-3 | 09:00-09:15 | Cascaded Propagation Technique for Fault Binary Decision<br>Diagram in Single-Event Transient Analysis<br>Jong Kang Park, Myoungha Kim, and Jong Tae Kim<br>School of Electronic and Electrical Engineering, Sungkyunkwan<br>University                                                            |

| WI1-N-4 | 09:15-09:30 | The Techniques for Exploiting The Plane-level Parallelism in<br>NAND Flash Based Storage Device<br>Wontaeck Jung <sup>1,2</sup> and Eui-Young Chung <sup>1</sup><br><sup>1</sup> School of Electrical and Electronic Engineering, Yonsei University,<br><sup>2</sup> Samsung Electronics Co., Ltd. |

| WI1-N-5 | 09:30-09:45 | Exploring Synchronous/Asynchronous Communication and<br>Computation for Mapping Streaming Applications onto CGRA-<br>based System<br>Hongsik Lee, Sangyun Oh, and Jongeun Lee<br>Department of Computer Science Ulsan National Institute of Science<br>and Technology                              |

| WI1-N-6 | 09:45-10:00 | Toward Neuromorphic Execution of Deep Learning Models<br>Taehwan Shin, Yongshin Kang, Seungho Yang, Seban Kim, and<br>Jaeyong Chung<br>Department of Electronic Engineering, Incheon National University                                                                                           |

## Power-Optimized Design of N:1 Serializer in 65-nm CMOS

Tongsung Kim and Woo-Young Choi

Department of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea E-mail: <u>tongsungk@gmail.com</u>

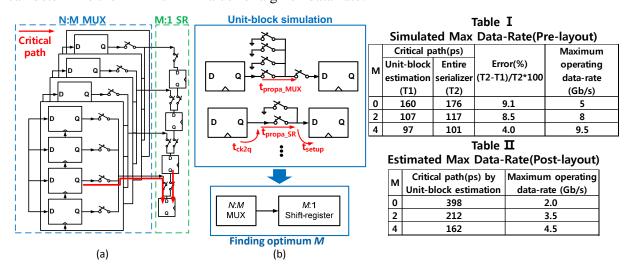

Power consumption optimization for serializers is very important for achieving high-performance SerDes systems. For optimal design, the serializer architeture as well as unit block structures must be carefully selected. In this paper, we present design methodology for determining the optimum structure of N:1 serializer in 65-nm CMOS technology. Serializers can be realized based on two different structures: multi-phase multiplexer (MUX) and shift register (SR). MUX is power-efficient but bandwidth limited, whereas SR is the opposite. Consequently, the front N:M serilizer should be realized with MUXs and the back M:1 with SRs as shown in Fig. 1(a). It is very important to determine the value of M for achieving optimal performance. The critical path can be analyzed so that the minimum value of M can be determined that provides the required operating data-rate. The critical path depends on each unit-block's timing delay and M. By simualting each unit-block shown in Fig. 1(b), the maximum operating data-rate of the entire serializer depending on M can be estimated. With this estimation, we can then determine the minumum M value with small effort for a given data rate. The verification of this approach is shown in Table I. The timing delay of critical path by unit-block estimation matches with that of the entire serializer within 9.1% error, which gives the estimated maximum operating data-rate. Table  $\Pi$ shows the estimated maximum operating data-rate with post-layout simulation. With this table, we can determine the minimum *M* value for a given data-rate.

Figure 1. (a) Block diagram of serializer (b) Unit-block simulation for finding optimum M